ModelSim SE 10.5 免费版是一款先进的数字电路模拟器,可以帮助电子工程师和硬件设计师快速验证他们的设计。首先,软件具有强大的仿真和调试功能,可以模拟各种数字电路,包括FPGA、ASIC、SoC等,以及多种数字信号处理和通信系统,而在仿真过程中,用户可以快速发现和调试设计中的问题,并通过波形分析和时序分析等工具,对电路的运行情况进行详细的分析和验证。其次,软件还具有先进的测试和验证工具,包括代码覆盖率分析、时序分析、波形分析、交互式调试等,而这些工具可以帮助用户快速发现和定位设计中的错误,并对电路的性能进行详细的分析和评估。最后,软件还支持多种仿真和调试方式,包括单步调试、断点调试、信号探头、触发器等,而·这些工具可以帮助用户更加灵活地控制仿真过程,并深入了解电路的运行情况。总之,如果你是一位电子工程师或者是硬件设计师的话,那么本软件你一定会喜欢的,毕竟它可以提升你的工作效率和设计质量。

ps:附带的破解补丁可完美激活软件,从而免费使用所有功能,但破解过程较为复杂,用户们可参考下文奉上的详细安装提问教程,希望对有需要的小伙伴们有所帮助。

modelsim10.5免费版安装教程

1、在本站下载解压,得到modelsim se 10.5原程序和Crack破解文件夹;

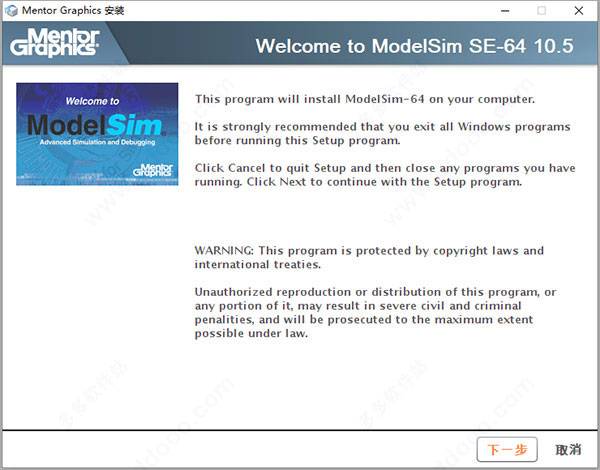

2、首先双击运行"modelsim-win64-10.5-se.exe"程序,进入软件安装向导;

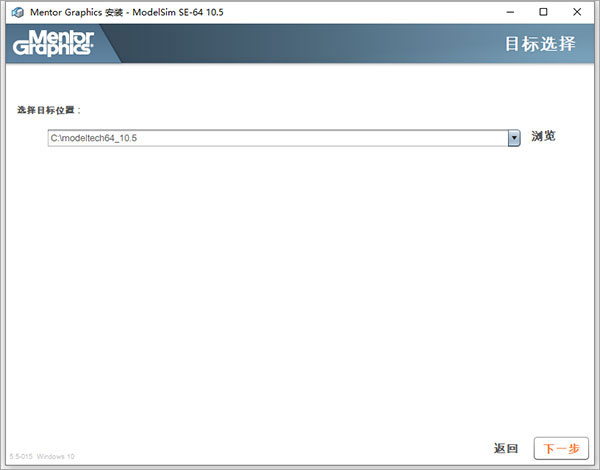

3、点击下一步,按默认目录进行安装;

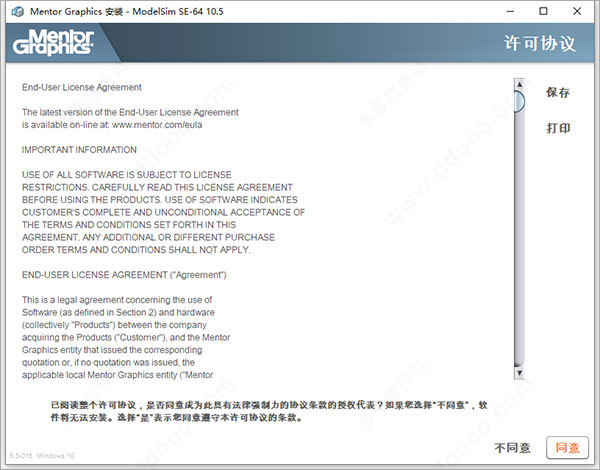

4、同意软件许可协议,依提示进行下一步;

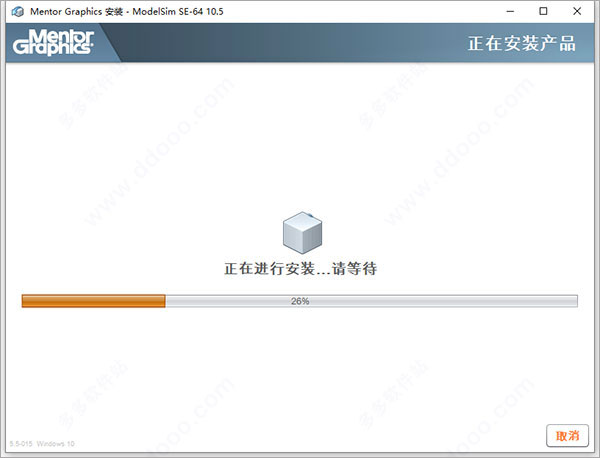

5、软件正在安装中,请用户耐心等待一小会;

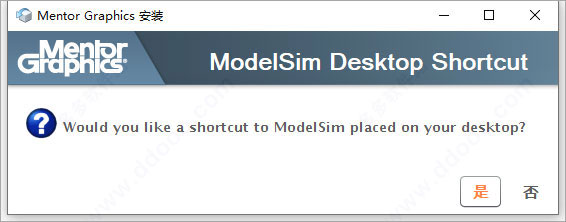

6、弹出窗口点击YES,创建桌面快捷方式;

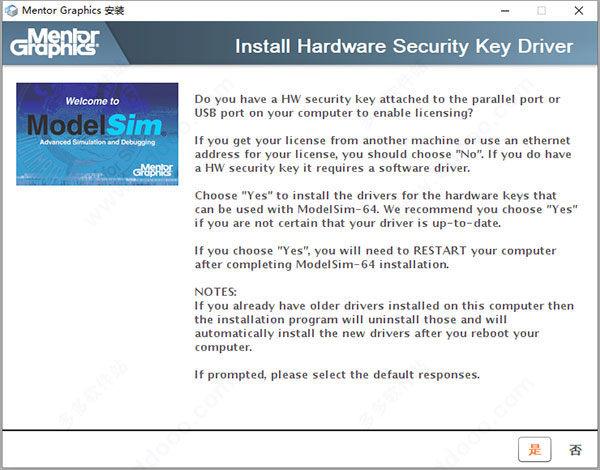

7、直到软件安装完成,如下图所示,先不要运行软件,点击否并退出安装向导;

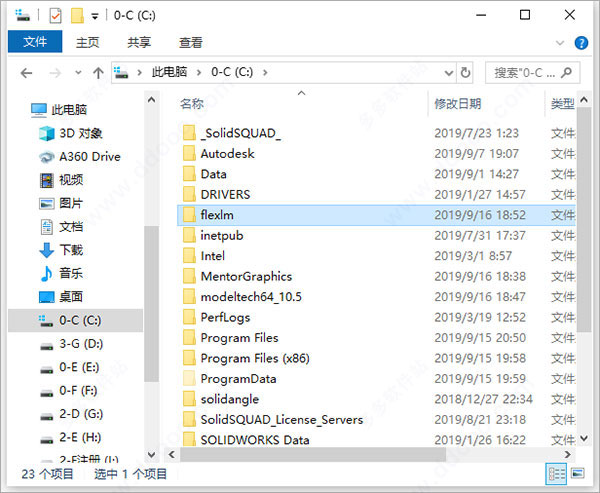

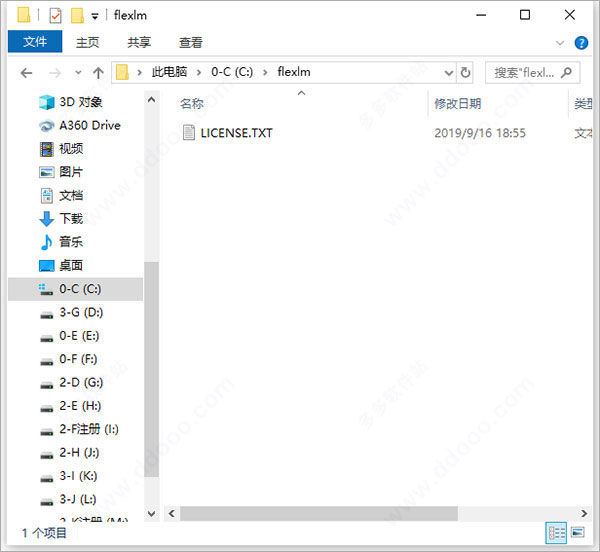

8、在C盘根目录下新建一个flexlm文件夹,如下图所示:

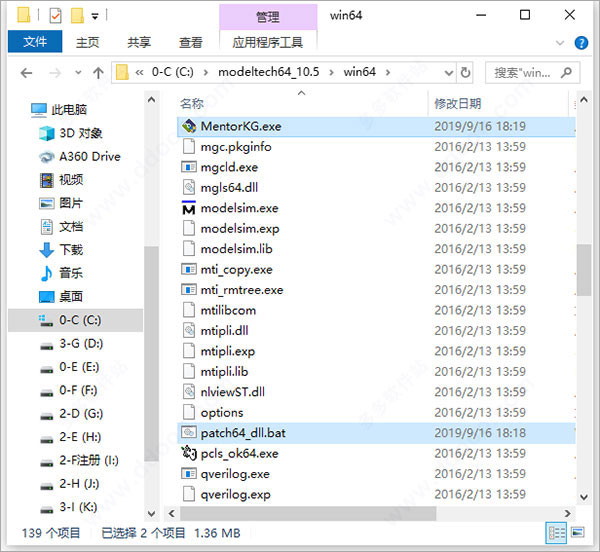

9、将Crack破解文件夹中的MentorKG.exe和patch64_dll.bat两个文件复制到软件安装目录下;

默认目录【C:modeltech64_10.5win64】

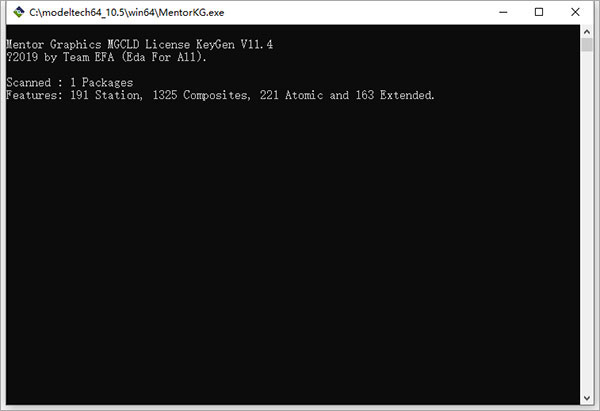

10、然后双击运行刚才复制过来的patch64_dll.bat程序;

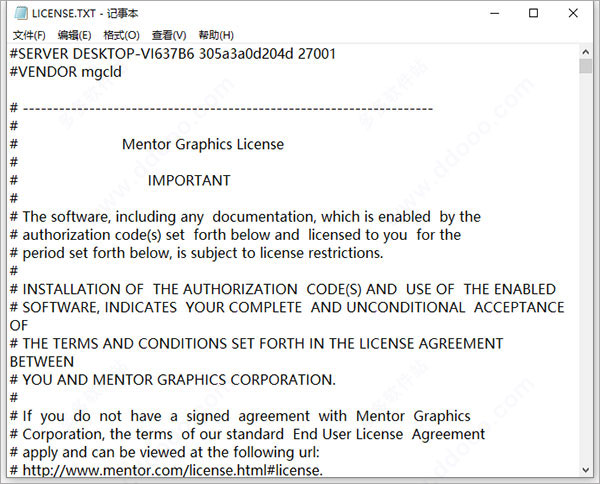

11、等待patch64_dll.bat程序完成之后,会弹出一个以LICENSE.TXT文件命名的记事本文件;

12、将LICENSE.TXT文件保存到C:flexlm文件夹中,如下图所示:

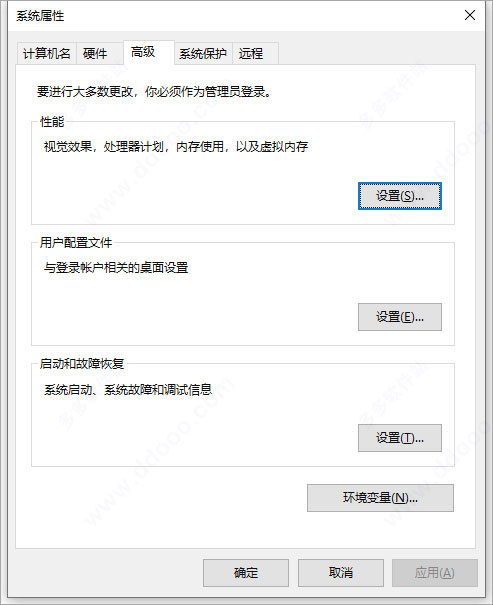

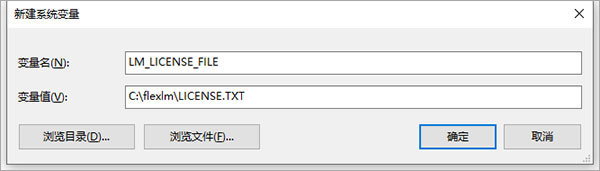

13、然后右击此电脑点击属性,进入高级系统设置;

14、打开系统“环境变量”选项,点击“新建”选项,在变量名中输入:LM_LICENSE_FILE,在变量值中输入:C:flexlmlicense.txt;

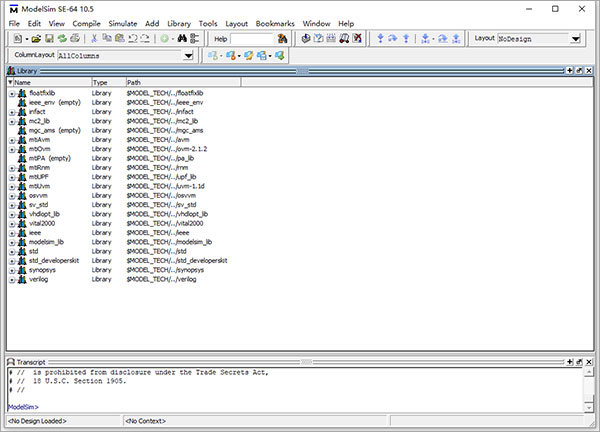

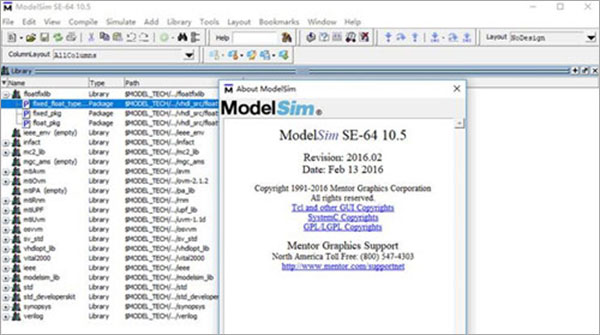

15、打开软件,即可软件已经成功激活啦,可以免费使用所有功能;

16、ok,以上就是modelsim se 10.5免费版详细安装教程。

软件特色

1、统一的混合语言模拟引擎,易于使用和性能

2、Verilog的原生支持,用于设计的SystemVerilog,VHDL和SystemC,用于有效验证复杂的设计环境

3、快速调试,易于使用,多语言调试环境

4、高级代码覆盖和分析工具,可实现快速覆盖范围

5、交互式和后期模拟调试可用,因此两者都使用相同的调试环境

6、强大的波形比较,便于分析差异和错误

7、统一覆盖数据库,具有完整的交互式和HTML报告和处理功能,可以在整个项目中理解和调试覆盖范

8、与HDL Designer和HDL Author相结合,可实现完整的设计创建,项目管理和可视化功能

功能介绍

1、高级代码覆盖率

ModelSim的高级代码覆盖功能和易用性降低了利用这一宝贵验证资源的障碍。

ModelSim高级代码覆盖功能为系统验证提供了有价值的指标。 所有覆盖信息都存储在统一覆盖数据库(UCDB)中,该数据库用于收集和管理高效数据库中的所有覆盖信息。 可以使用分析代码覆盖率数据的覆盖率实用程序,例如合并和测试排名。 覆盖结果可以交互式查看,模拟后或多次模拟运行合并后查看。 代码覆盖度量可以按实例或设计单位报告,从而提供管理覆盖数据的灵活性。

支持的覆盖类型包括:

声明报道

运行期间执行的语句数

分行报道

影响HDL执行控制流的表达式和case语句

条件覆盖

将分支上的条件分解为使结果为true或false的元素

表达范围

与条件覆盖相同,但涵盖并发信号分配而不是分支决策

重点关注表达

以确定覆盖结果的表达式的每个独立输入的方式呈现表达覆盖率数据

增强的切换覆盖范围

在默认模式下,计数从低到高和从高到低的转换;在扩展模式下,计算与X的转换

有限状态机覆盖

州和州的过渡覆盖范围

2、混合HDL仿真

ModelSim将仿真性能和容量与模拟多个模块和系统以及实现ASIC门级别签核所需的代码覆盖和调试功能相结合。 全面支持Verilog,SystemVerilog for Design,VHDL和SystemC为单语言和多语言设计验证环境提供了坚实的基础。 ModelSim易于使用且统一的调试和仿真环境为当今的FPGA设计人员提供了他们不断增长的高级功能以及使他们的工作高效的环境。

3、有效的调试环境

ModelSim调试环境为Verilog,VHDL和SystemC提供了广泛的直观功能,使其成为ASIC和FPGA设计的首选。

ModelSim通过智能设计的调试环境简化了发现设计缺陷的过程。 ModelSim调试环境有效地显示设计数据,以便分析和调试所有语言。

ModelSim允许在保存结果的仿真后以及实时仿真运行期间使用许多调试和分析功能。例如,coverage查看器使用代码覆盖率结果分析和注释源代码,包括FSM状态和转换,语句,表达式,分支和切换覆盖率。

信号值可以在源窗口中注释并在波形查看器中查看,从而简化了对象及其声明之间以及访问文件之间的超链接导航的调试导航。

可以在列表和波形窗口中分析竞争条件,增量和事件活动。可以轻松定义用户定义的枚举值,以便更快地了解模拟结果。为了提高调试效率,ModelSim还具有图形和文本数据流功能。

ModelSim与Mentor的旗舰模拟器Questa®共享一个共同的前端和用户界面。这使客户可以轻松升级到Questa,因为他们需要更高的性能并支持高级验证功能。